Context Switch

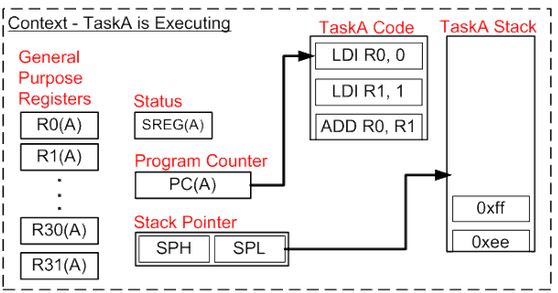

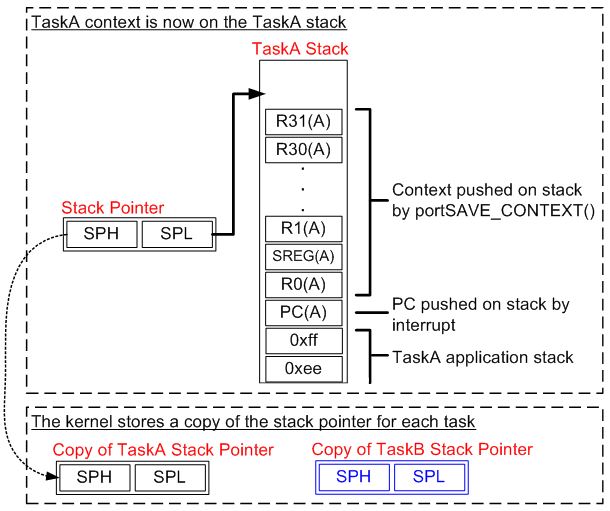

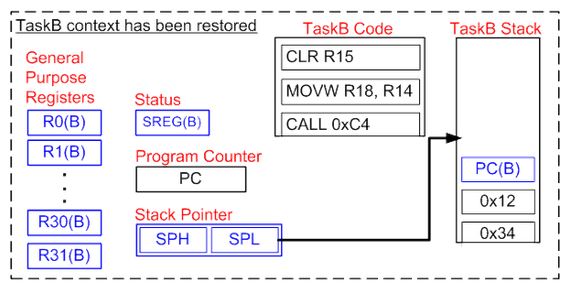

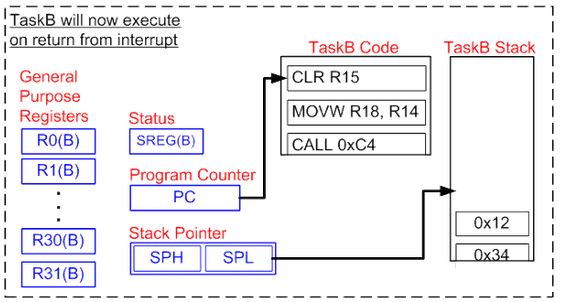

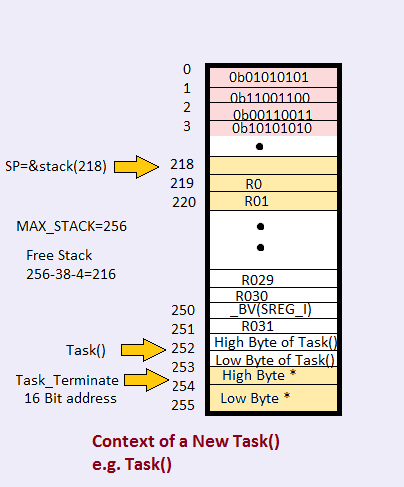

In this page we will describe the data that constitute the context of a task in an 8 bit AVR ATmel

MCU. We will then

show how the kernel switches the contexts of tasks to provide concurrency.

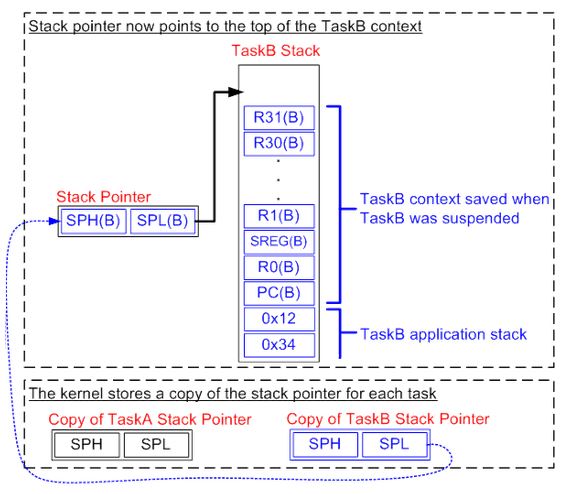

In general, the scheduler maintains a queue of tasks for each priority level (e.g., System, Periodic, RR). Based on some scheduling policies (fixed or dynamic) the scheduler may decide to suspend a task and resume another task, that is, switch contexts to run a different task. In this RTOS, a context switch occurs in the following cases:

In general, the scheduler maintains a queue of tasks for each priority level (e.g., System, Periodic, RR). Based on some scheduling policies (fixed or dynamic) the scheduler may decide to suspend a task and resume another task, that is, switch contexts to run a different task. In this RTOS, a context switch occurs in the following cases:

- an RR task pre-empts the idle task,

- an RR task finishes its quantum (allotted time of execution),

- a scheduled Periodic task pre-empts an RR or the idle task,

- a Periodic task voluntarily relinquishes the CPU,

- a System task becomes ready and pre-empts a running non-system task (e.g., Periodic, RR, idle)

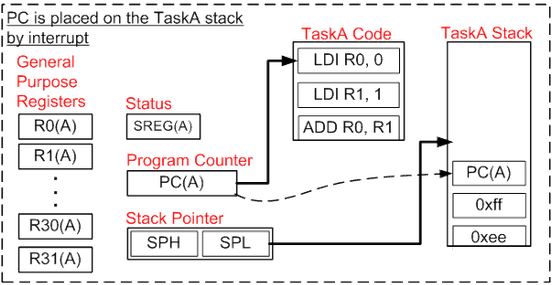

- an RTOS tick occurs, and

- a hardware interrupt pre-empts a running task.